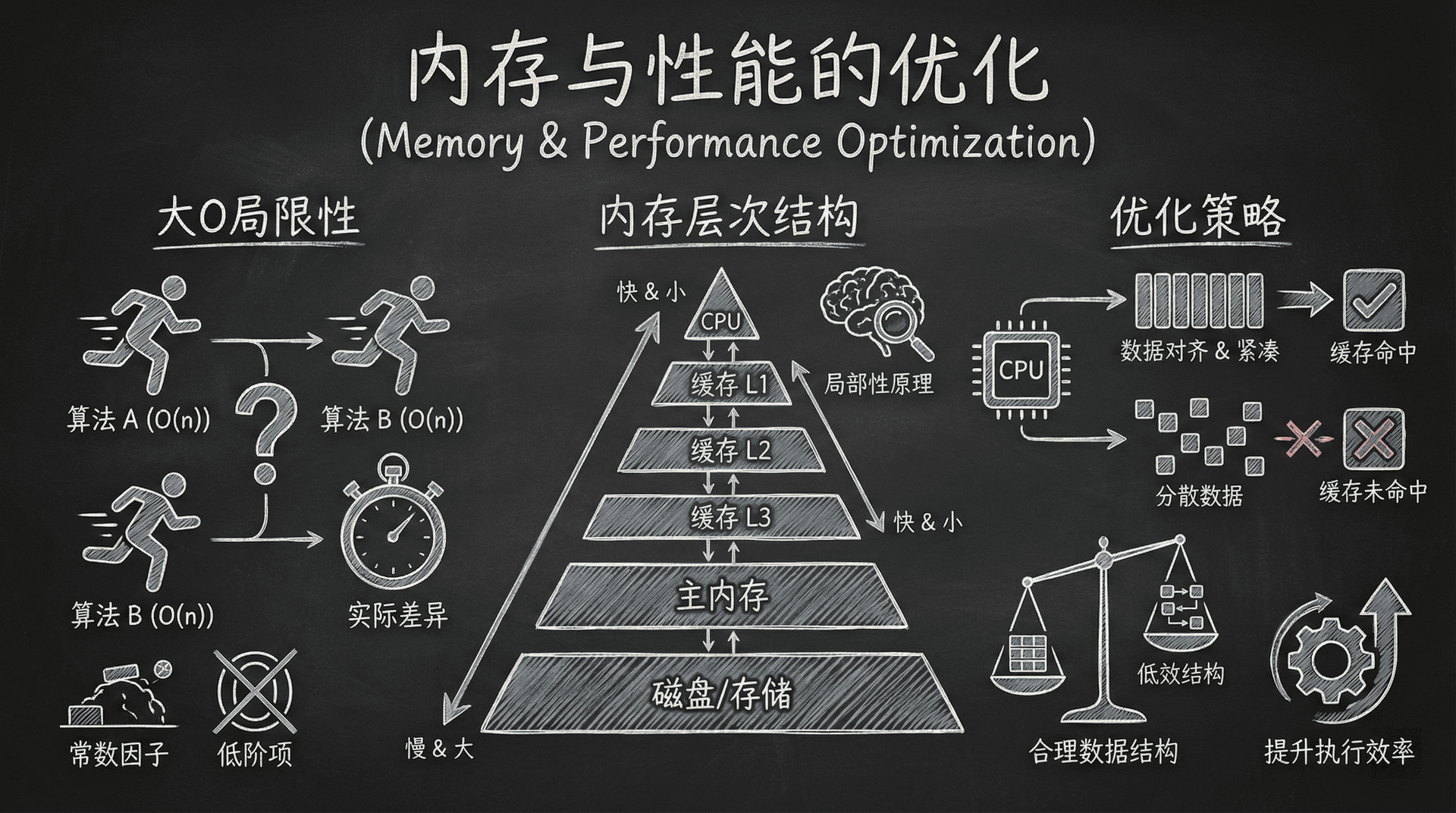

内存与性能的优化

在数据结构与算法的学习中,大O表示法为我们提供了算法复杂度的宏观视角,帮助我们理解算法性能随输入规模增长的变化趋势。大O表示法告诉我们,一个的线性算法在理论上要优于一个的二次算法。

然而,当我们面对两个同样具有时间复杂度的算法时,大O表示法无法区分它们的实际性能差异。在真实世界的基准测试中,这两个算法可能表现出数倍甚至数十倍的性能差异。这种差异源于大O表示法为了简化分析而忽略的常数因子和低阶项,而这些被忽略的因素恰恰是决定程序实际运行效率的关键。

在这一部分,我们将深入探索计算机系统的内存层次结构,分析数据在内存中的组织方式如何影响程序的执行效率。我们将从CPU缓存系统的工作原理出发,理解局部性原理如何被硬件利用,以及如何通过合理的数据结构选择和数据对齐策略来优化程序性能。

内存层次结构

现代计算机系统采用分层的内存架构,这种设计基于一个核心原则:存储容量越大,访问延迟越高,但单位成本越低。这种权衡使得系统能够在成本可控的前提下,通过多级缓存机制显著提升整体性能。

内存层次结构遵循一个基本规律:距离CPU越近的存储层级,容量越小,但访问速度越快,单位成本也越高。

现代x86-64架构的典型内存层次结构包括以下层级:

- 寄存器(Registers):位于CPU内部,是访问速度最快的存储单元。现代处理器通常拥有几十个通用寄存器,每个寄存器可以存储一个机器字长(64位系统为8字节)。寄存器的访问延迟小于1纳秒,但数量极其有限,通常只有几十个。

- L1缓存(Level 1 Cache):分为指令缓存(L1I)和数据缓存(L1D),通常各为32KB,访问延迟约为1纳秒。L1缓存位于CPU核心内部,每个核心拥有独立的L1缓存。

- L2缓存(Level 2 Cache):容量通常在256KB到1MB之间,访问延迟约为10纳秒。L2缓存同样位于CPU核心内部,每个核心拥有独立的L2缓存。

- L3缓存(Level 3 Cache):也称为最后一级缓存(LLC,Last Level Cache),容量通常在8MB到32MB之间,访问延迟约为40纳秒。L3缓存在多核处理器中通常被所有核心共享。

- 主内存(Main Memory / RAM):容量从几GB到数百GB不等,访问延迟约为100纳秒,比L1缓存慢约100倍。

- 辅助存储(Secondary Storage):包括机械硬盘(HDD)和固态硬盘(SSD)。HDD的访问延迟约为10毫秒,SSD的访问延迟约为100微秒,比主内存慢数个数量级。

这种巨大的延迟差异(从纳秒级到毫秒级,跨越了六个数量级)使得缓存命中率成为决定程序性能的关键因素。当CPU需要访问某个数据时,如果该数据已经存在于L1、L2或L3缓存中,我们称之为缓存命中(Cache Hit),访问可以在纳秒级完成。如果数据不在任何缓存层级中,CPU必须访问主内存,这称为缓存未命中(Cache Miss),会导致数百个CPU周期的等待。

在高性能计算场景中,缓存未命中带来的性能损失是巨大的。一次L1缓存命中需要约1个CPU周期,而一次主内存访问可能需要200-300个CPU周期。这意味着,即使两个算法具有相同的时间复杂度,如果其中一个算法的缓存命中率更高,其实际执行时间可能显著优于另一个算法。

局部性原理

局部性原理(Locality Principle)是计算机系统设计的基础理论之一,它描述了程序访问数据的时空特征。硬件设计者利用这一原理,通过多级缓存和预取机制来提升系统性能。

局部性原理包含两个核心概念:时间局部性(Temporal Locality)和空间局部性(Spatial Locality)。

时间局部性指的是:如果一个内存位置被访问,那么在不久的将来,这个位置很可能再次被访问。这种特性在循环结构、函数调用栈和频繁使用的变量中表现得尤为明显。例如,在循环中反复访问同一个计数器变量,或者在递归函数中反复访问栈上的局部变量,都体现了时间局部性。

空间局部性指的是:如果一个内存位置被访问,那么其附近的内存位置很可能在不久的将来被访问。这种特性在顺序访问数组、遍历链表节点、访问结构体成员等场景中都有体现。当我们访问数组元素arr[i]时,很可能接下来会访问arr[i+1],这就是空间局部性的典型表现。

现代CPU的缓存系统充分利用了空间局部性原理。当发生缓存未命中时,CPU不会只从主内存读取请求的那个数据,而是会读取一个连续的、固定大小的内存块,这个内存块被称为缓存行(Cache Line)。在x86-64架构中,缓存行的标准大小为64字节。

这种设计带来的性能提升是显著的。假设我们正在遍历一个整数数组,每个整数占4个字节。当我们第一次访问arr[0]时,会发生缓存未命中,CPU需要从主内存读取数据。由于缓存行机制,CPU会一次性将arr[0]到arr[15](共64字节,16个整数)全部加载到缓存中。接下来访问arr[1]到arr[15]时,都会发生缓存命中,访问速度提升数百倍。

理解局部性原理是编写高性能代码的基础:我们应该尽量让数据的访问模式符合时间局部性和空间局部性,使得CPU的缓存预取机制能够高效工作,最大化缓存命中率。

除了硬件自动的缓存行预取,现代CPU还配备了硬件预取器(Hardware Prefetcher),它能够识别程序的内存访问模式(如顺序访问、步长访问等),并提前将可能被访问的数据加载到缓存中。对于顺序访问数组这样的访问模式,硬件预取器能够非常有效地工作,进一步提升了缓存命中率。

数据结构的内存布局与缓存性能

不同的数据结构在内存中的组织方式直接影响着程序的缓存性能。即使两个数据结构在算法复杂度上相同,它们在真实硬件上的表现可能差异巨大。

数组与std::vector:缓存友好的连续存储

数组和C++标准库中的std::vector采用连续的内存布局,所有元素按照索引顺序依次存储在内存的连续地址空间中。这种布局方式完美契合了空间局部性原理,使得顺序访问数组时能够获得极高的缓存命中率。

当我们顺序遍历一个数组时,访问模式呈现出完美的空间局部性:访问完arr[i]后,紧接着访问arr[i+1],这两个元素在内存中相邻,很可能位于同一个缓存行中。第一次访问某个缓存行时可能发生缓存未命中,但后续访问该缓存行中的其他元素时都会发生缓存命中,整体缓存命中率通常可以达到90%以上。

|#include <vector> #include <numeric> #include <iostream> #include <chrono> /** * 演示数组顺序访问的缓存友好特性 * 顺序访问模式能够充分利用空间局部性,获得极高的缓存命中率 */ void arrayPerformanceDemo() { const size_t SIZE = 10000000; // 一千万个整数,约40MB数据 std::vector<int> data(SIZE); // 初始化数组 std::iota(data.begin(), data.end

这种高效的访问模式使得CPU的硬件预取器能够非常准确地预测下一步的访问地址,提前将数据加载到缓存中,进一步提升了性能。

链表

链表采用完全不同的内存布局策略。链表中的每个节点在内存中的位置是动态分配的,节点之间通过指针连接,但节点本身在内存中的分布可能是随机的、非连续的。这种布局方式严重违背了空间局部性原理。

当我们遍历一个链表时,访问模式呈现出极差的空间局部性:访问完节点node[i]后,需要通过next指针找到node[i+1]的地址,而这个地址与node[i]的地址可能相距甚远,甚至位于完全不同的内存页中。

每次访问新节点时,都可能发生缓存未命中,因为该节点所在的内存区域之前从未被访问过,不在任何缓存层级中。

|#include <list> #include <iostream> #include <chrono> /** * 演示链表遍历的缓存不友好特性 * 随机内存访问模式导致频繁的缓存未命中 */ void listPerformanceDemo() { const size_t SIZE = 10000000; std::list<int> data; // 初始化链表 for (int i = 0; i < SIZE; ++i) { data.

这就是为什么,虽然遍历数组和遍历链表在算法复杂度上都是,但在实际性能测试中,遍历链表可能比遍历数组慢5到10倍。 这种性能差异完全来自于缓存命中率的差异:数组的高缓存命中率使得大部分内存访问都在纳秒级的缓存中完成,而链表的低缓存命中率使得大量访问需要等待数百个CPU周期的主内存访问。

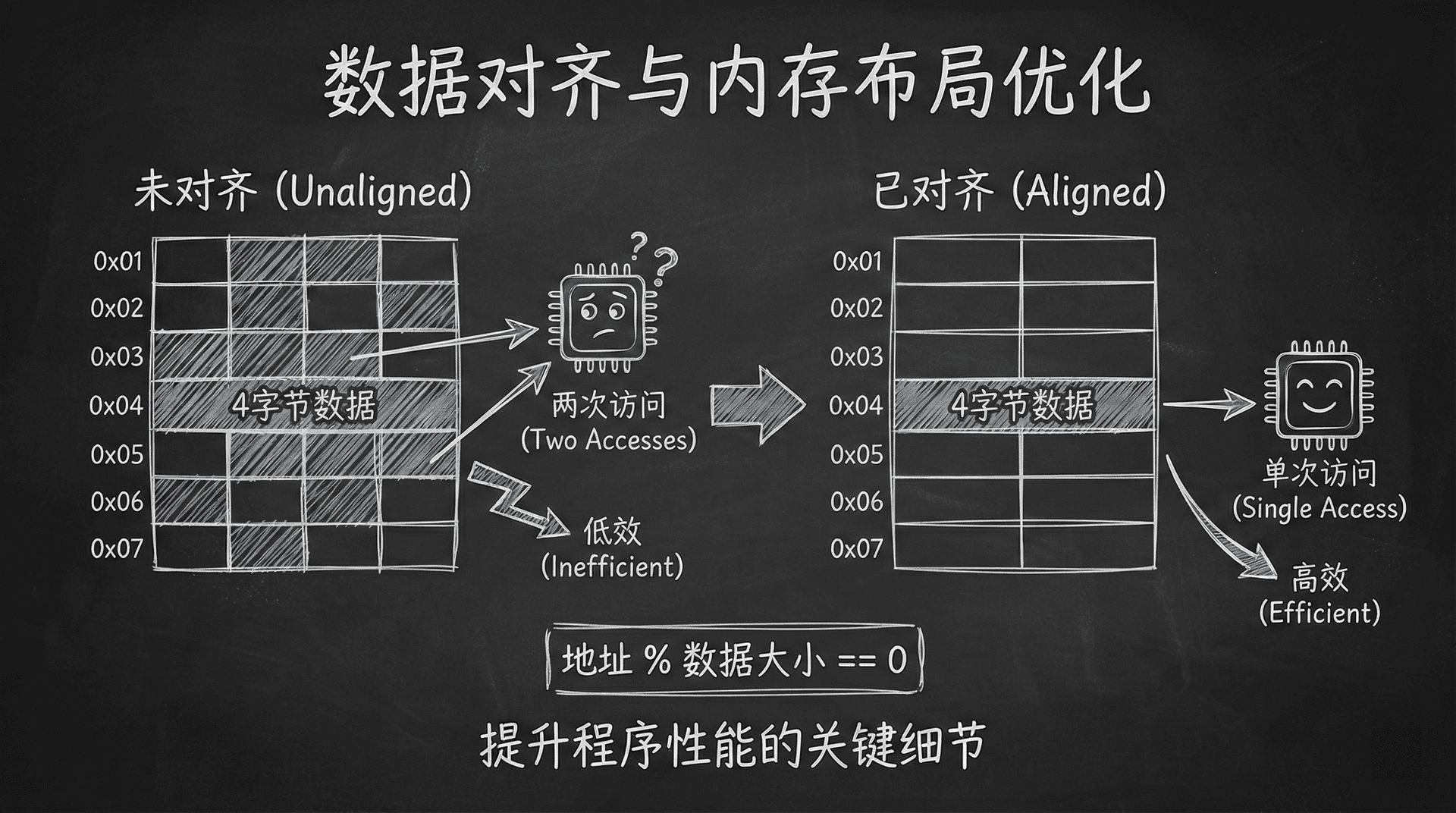

数据对齐与内存布局优化

除了数据结构的连续性问题,数据在内存中的对齐方式也会显著影响程序的性能。数据对齐(Data Alignment) 是指将数据存放在内存地址为其大小的整数倍的位置上。

对齐的硬件原理

现代CPU通过内存总线访问内存,内存总线的宽度通常是64位(8字节)或更宽。当CPU需要读取一个未对齐的数据时(例如,一个8字节的double类型数据存放在地址0x1005,而不是8的倍数地址),CPU可能需要进行两次内存访问:一次读取包含数据前半部分的8字节,另一次读取包含数据后半部分的8字节,然后在CPU内部将两部分拼接起来。这个过程不仅增加了内存访问次数,还增加了CPU的计算开销。

在某些架构(如某些ARM处理器)上,未对齐的内存访问甚至会导致硬件异常,程序直接崩溃。在x86-64架构上,虽然允许未对齐访问,但性能损失仍然显著。

数据对齐规则:一个大小为字节的数据类型,应该存放在地址为的整数倍的内存位置上。例如,4字节的

int应该存放在4的倍数地址上,8字节的double应该存放在8的倍数地址上。

结构体成员对齐与填充

C++编译器会自动处理基本数据类型的对齐,但当我们定义结构体或类时,成员变量的声明顺序会影响结构体的内存布局和总大小。为了满足对齐要求,编译器会在成员变量之间插入填充字节(Padding),这可能导致结构体的实际大小大于其成员变量大小的简单相加。

|#include <iostream> /** * 演示结构体成员对齐对内存布局的影响 * 成员变量的声明顺序直接影响结构体的大小 */ // 方案一:成员顺序导致大量填充 struct BadAlignment { char a; // 1字节,起始地址0 // 编译器插入7字节填充,使double对齐到8的倍数 // (7 bytes padding) double b; // 8字节,起始地址8 int c; // 4字节,起始地址16 // 编译器插入4字节填充,使结构体总大小为最大成员(8字节)的倍数 // (4 bytes padding) // 总大小: 24字节 }; // 方案二:优化后的成员顺序 struct GoodAlignment { double b;

结构体成员对齐的最佳实践:按照成员变量的大小从大到小排序,通常能够最小化填充字节,得到最紧凑的内存布局。这个规则不是绝对的,但在大多数情况下都能有效减少内存占用。

伪共享问题

在多核处理器系统中,还存在一个与缓存相关的性能问题:伪共享(False Sharing)。当两个不同的CPU核心频繁访问位于同一个缓存行中的不同数据时,即使它们访问的是完全独立的数据,也会因为缓存一致性协议(如MESI协议)而导致缓存行在核心之间频繁传递,造成性能损失。

例如,如果我们有一个包含多个线程计数器的数组,每个线程更新自己的计数器,但这些计数器恰好位于同一个64字节的缓存行中,那么即使线程之间没有数据依赖,也会因为缓存行的共享而导致性能下降。解决方法是确保频繁访问的数据之间有足够的间隔,或者使用编译器指令(如alignas(64))来强制对齐到缓存行边界。

数据对齐可视化

性能优化实践

理解了内存层次结构和局部性原理后,我们可以通过以下策略来优化程序性能:

优先使用连续存储的数据结构:在需要频繁遍历的场景中,优先选择std::vector而非std::list。即使std::list在某些操作(如中间插入)上具有更好的算法复杂度,但在实际性能测试中,std::vector的缓存友好特性往往能够带来更好的整体性能。

优化数据访问模式:尽量让数据访问呈现出良好的空间局部性。例如,在二维数组遍历时,按照行优先顺序访问通常比按列优先顺序访问更高效,因为行优先访问能够更好地利用缓存行。

合理设计结构体布局:按照成员变量大小从大到小排序,最小化填充字节。这不仅能够节省内存,还能提高缓存利用率(更紧凑的数据意味着更多的数据能够装入同一级缓存)。

避免不必要的内存分配:频繁的内存分配和释放不仅会导致堆碎片化,还可能破坏数据的空间局部性。在性能关键路径上,考虑使用对象池或预分配策略。

小练习

- 顺序访问数组元素(如 arr[i])主要体现了哪种局部性原理?

- 从缓存性能角度,游戏排行榜系统应该选择vector还是list?

- 为了最小化结构体内存占用,应该按照什么顺序排列成员变量?